Pravidla návrhu desek plošných spojů: Vedení a přeslechy

Rychle se rozvíjející oblast elektroniky a její vysoká poptávka dnes vede k zásadnímu požadavku – co nejmenší rozměry elektroniky s vysokou rychlostí, ideálně na jednovrstvé DPS.

Pravidla návrhu desek plošných spojů: Vedení a přeslechy

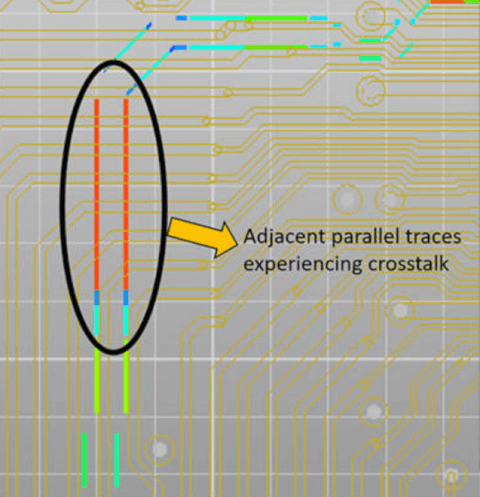

Rychle se rozvíjející oblast elektroniky a její vysoká poptávka dnes vede k zásadnímu požadavku – co nejmenší rozměry elektroniky s vysokou rychlostí, ideálně na jednovrstvé DPS. Stále se zmenšující prostor nevyhnutelně vede k jedinému, a to k přibližování vodivých cest blíže k sobě, čím se sice redukuje prostor na DPS, ale může to způsobit také fatální problémy. Elektromagnetická vazba vodivých cest neboli přeslech na DPS je dnes velmi aktuální téma, které Ansys dokáže odhalit ještě před zahájením prototypové výroby (obrázek 1).

Obrázek 1 Potenciální problém přeslechů vodivých cest na DPS

Přestože zmenšování rozměrů se dnes již prakticky nelze vyhnout, existují jistá pravidla při návrhu DPS, která mohou značně snížit riziko vzniku přeslechů, a tím i předejít problémům v certifikované EMC komoře. V první části ohledně návrhu DPS jsme si již ukázali několik pravidel, dnes tyto typy doplníme o několik dalších principů a také se podíváme na to, jak pomocí Ansys SIwave DPS analyzovat, a tím předejít možným problémům s EMC/ EMI.

(Pojem „kritická síť“ v následující části odkazuje na vysokorychlostní hodinové/datové, snímací linky dle aplikace DPS.)

Pravidlo 1: Kritická síť blízko vstupní sítě

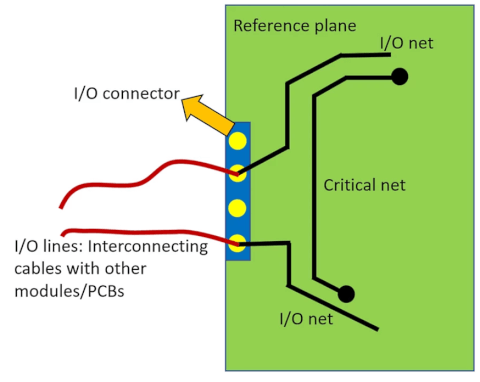

Velice důležité je sledovat kritické sítě ve vztahu ke vstupně/výstupním (I/O) zařízením, protože šum se velice době přenáší mezi deskami pomocí I/O portů (obrázek 2) uvnitř kompletního systému DPS.

Obrázek 2 Příklad krátké vzdálenosti mezi kritickou sítí a vstupně/výstupním zařízením

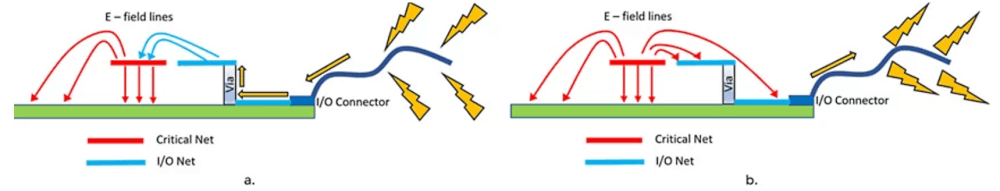

Šum, který vstupuje do desky přes I/O vedení, může zapříčinit vznik vazby s kritickou sítí, jež přenáší důležitá data nebo hodinové signály, jedná se o tzv. imunitu DPS (obrázek 3a). V podobném sledu, veškeré vysokorychlostní signály přenášené kritickou sítí můžou pomocí vazby přes I/O vedení vystupovat ven z DPS do okolního světa, a tak ovlivnit ostatní elektronická zařízení. Tento efekt se nazývá emise DPS (obrázek 3b).

Obrázek 3a: Imunita DPS; Obrázek 3b: Emise DPS

Pravidlo 2: Délka vodivé neizolované stopy

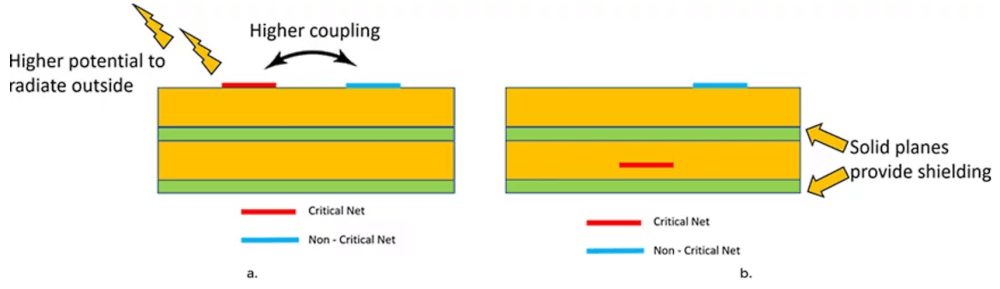

U vysokorychlostních DPS (> 100 MHz), kde jsou kratší vlnové délky, je každá kritická síť (obrázek 4a) dostatečně dlouhá na to, aby se z ní stal ideální zářič (anténa), zvláště pokud je odkrytá na horní nebo spodní vrstvě. Toto záření může způsobit nežádoucí vazbu se sousední stopou nebo dokonce s kabely, které jsou blízko této stopy. Doporučuje se tedy zapustit kritické sítě mezi vrstvy do DPS, viz. obrázek 4b, čímž návrhář zatlumí pole vyzářené stopou, a zabrání tak neúmyslným přeslechům a problémům s EMI. Pokud ovšem musíte stopy zachovat odkryté, snažte se dodržet co nejmenší délku odkrytých částí, poněvadž čím bude odkrytá část menší, tím bude potenciální nežádoucí anténa méně účinná.

Obrázek 4a: Odkrytá kritická síť na DPS; Obrázek 4b: Zapuštěná kritická síť do DPS

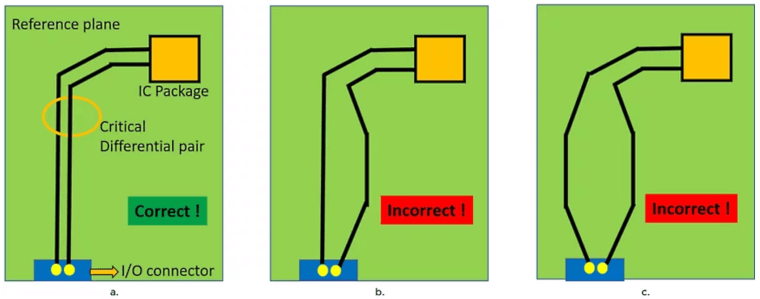

Pravidlo 3: Diferenciální páry

Dle teorie mají signály přenášené pomocí diferenciálních párů stejnou velikost, ale opačnou polaritu, což znamená, že potenciální interference se buď vyruší, nebo jsou zanedbatelné. To ovšem platí pouze za předpokladu dodržení stejné délky, symetrického vedení a umístění co nejblíže k sobě, přičemž porušení těchto předpokladů vede ke vzniku šumu a potenciálním problémům s EMI. Tento problém se obvykle řeší u vysokofrekvenčních DPS, protože s vyšší frekvencí signálů je potenciální problém s EMI daleko vyšší. Na obrázku 5 je znázorněno několik různých správných/špatných způsobů vedení diferenciálního páru mezi pouzdrem integrovaného obvodu a výstupním bodem na desce (konektor).

Obrázek 5a: Správné vedení diferenciálního páru na DPS; Obrázek 5b/5c: Špatné vedení diferenciálního páru na DPS

Diferenciální páry: Simulace a vztah k aktuálním požadavkům na testy

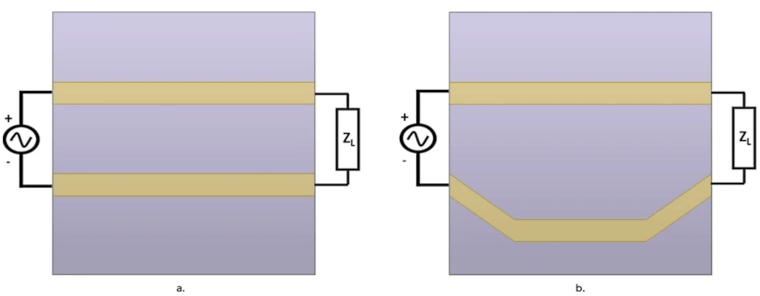

Na obrázku 6a, respektive 6b, je pro ilustraci zobrazen jednoduchý scénář diferenciálního páru na DPS, kde je symetrické, respektive nesymetrické uspořádání páru připojeno ke zdroji střídavého napětí na jednom konci a na druhém konci je připojeno na definovanou zátěž.

Obrázek 6a: Symetrické zapojení diferenciálního páru; Obrázek 6b: Nesymetrické zapojení diferenciálního páru

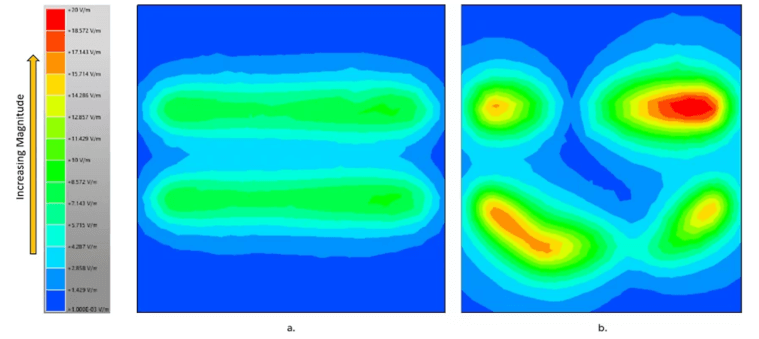

Díky analýze blízkého pole v Ansys SIwave je patrné, že v případě symetrického páru je úroveň blízkého pole mnohem nižší než v případě nesymetrického páru (obrázek 7a, respektive 7b).

Obrázek 7a: Blízké pole na DPS při symetrickém zapojení;

Obrázek 7b: Blízké pole na DPS při nesymetrickém zapojení diferenciálního páru

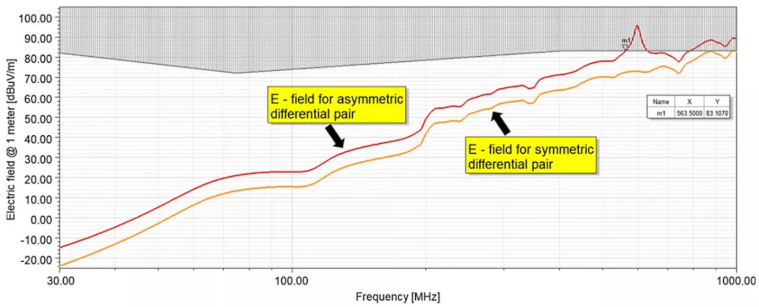

Za předpokladu, že na této DPS musíme provést test EMI/EMC podle normy UNECE R10 (v Evropě) s požadavkem na vyzařované emise, obrázek 8 představuje porovnání výsledků simulace dalekého pole od DPS ve vzdálenosti 1 m ve frekvenčním pásmu 30 MHz až 1 GHz pro symetrické i nesymetrické zapojení. Z výsledků je patrné, že nesymetrické zapojení způsobuje cca o 8–10 dB vyšší vyzařování, a tudíž neshodu s normou na frekvenci 563.50 MHz.

Obrázek 8: Vyzařované emise ve vzdálenosti 1 m od DPS pro symetrické a nesymetrické zapojení

Díky programu Ansys SIwave je možné odhalit problémy s EMI, optimalizovat design a ušetřit na fyzických testech ještě před tím, než bude vyroben prototyp.

Další články

Využití PyFluent a strojového učení pro udržitelné zpracování materiálů

Tento článek odhaluje, jak mohou moderní technologie a kreativní přístup přispět k vývoji ekologičtějších výrobních…

Zlepšete své simulace pomocí modelů redukovaného řádu a digitálních dvojčat

V dynamické oblasti inženýrských simulací zůstává dosažení efektivity a přesnosti neustálou výzvou.

Efektivní využití restartování analýzy v prostředí Ansys Mechanical

Článek se zabývá možnostmi restartování analýz v softwaru Ansys Mechanical, které umožňují efektivnější správu…